Time Left - 20:00 mins

GATE CS : Digital Logic Champion Quiz 3

Attempt now to get your rank among 421 students!

Question 1

In the following J-K flip-flop we have  AND k=1. Assuming the flip-flop was initially cleared and then clocked for 6 pulses, the sequence at the Q output will be

AND k=1. Assuming the flip-flop was initially cleared and then clocked for 6 pulses, the sequence at the Q output will be

Question 2

Figure shows a mod-K counter. Here K is equal to

Question 3

The initial state of MOD-16 down counter is 0110. After 37 clock pulses, the state of the counter will be

Question 4

Match List-I with List-II and select the correct answer using the codes given below the lists:

List-I

A- Shift register

B- Counter

C- Decoder

List-II

1- Frequency division

2- Addressing in memory chips

3- Serial to parallel data conversion

List-I

A- Shift register

B- Counter

C- Decoder

List-II

1- Frequency division

2- Addressing in memory chips

3- Serial to parallel data conversion

Question 5

A 3-bit ripple counter uses J-K flipflops. If the propagation delay of each flipflop is 50 n sec, then what will be the maximum clock frequency that can be used in megahertz?

Question 6

The reduced state table of a sequential machine has 7 rows. What is the minimum number of flip-flops needed to implement the machine?

Question 7

The clock frequency applied to the digital circuit shown in the figure below is 1 kHz. If the initial state of the output Q of the flip-flop is '0', then the frequency of the output waveform Q in kHz is

Question 8

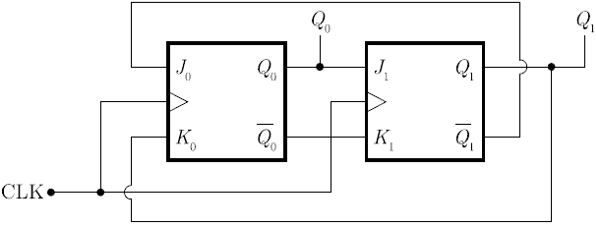

In the following sequential circuit, the initial state (before the first clock pulse) of the circuit is (Q1,Q0) = 00. The state Q1Q0, immediately after the 333rd clock pulse is

Question 9

Following pulse is applied to an SR flip flop.

If ∆t is propagation delay, which of the following relations should hold to avoid the rave condition?

If ∆t is propagation delay, which of the following relations should hold to avoid the rave condition?

Question 10

Consider the following statements in Johnson counter:

1) A MOD-6 Johnson counter requires 3 FFs.

2) Johnson counter requires decoding gates.

3) To decode each count, one logic gate is used. Each gate requires only two inputs regardless of the number of FFs.

Which of these statements are correct?

1) A MOD-6 Johnson counter requires 3 FFs.

2) Johnson counter requires decoding gates.

3) To decode each count, one logic gate is used. Each gate requires only two inputs regardless of the number of FFs.

Which of these statements are correct?

- 421 attempts

- 7 upvotes

- 16 comments

Apr 19GATE & PSU CS