Time Left - 01:00:00 mins

GATE CS : Digital Logic - National Champion Test

Attempt now to get your rank among 751 students!

Question 1

The number of distinct Boolean expression of 4 variables is

Question 2

The greatest negative number which can be stored in a 8 – bit register using 2’s complement arithmetic is

Question 3

Which of the following subtraction operations results in F16?

(1) (BA)16 – (AB)16

(2) (BC)16 – (CB)16

(3) (CB)16 – (BC)16

Select the correct answer using the code given below:

(1) (BA)16 – (AB)16

(2) (BC)16 – (CB)16

(3) (CB)16 – (BC)16

Select the correct answer using the code given below:

Question 4

If (2.3)base4 + (1.2)base4 = (y)base4; what is the value of y?

Question 5

The output of the 4-to-1 MUX shown in below is

Question 6

A bulb in a staircase has two switches, one switch being at the ground floor and the other one at the first floor. The bulb can be turned ON and also can be turned OFF by any one of the switches irrespective of the state of the other switch. The logic of switching of the bulb resembles

Question 7

What is the Boolean expression for the truth table shown below?

Question 8

Race-around condition occurs in

Question 9

The Boolean expression

can be simplified to

can be simplified to

Question 10

A ripple counter with n flip-flops can function as a

Question 11

For the circuit shown in the following figure, the Boolean expression for the output Y in terms of inputs P, Q, R and S is

Question 12

A 4-bit synchronous counter has flip-flops having propagation delay of 50 ns each and AND gates having propagation delay of 20 ns each. The maximum frequency of clock pulses can be

Question 13

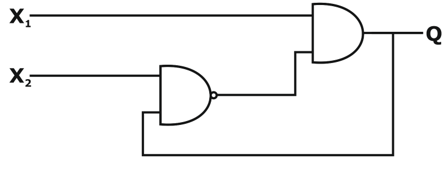

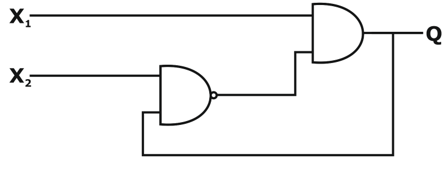

In the following figure, as long as X1 = 1 and X2= 1, the output Q remains

Question 14

The reduced state table of a sequential machine has 7 rows. What is the minimum number of flip-flops needed to implement the machine?

Question 15

The figure shows a digital circuit constructed using negative edge triggered J-K flip flops. Assume a starting state Q2Q1Q0 = 000. This state Q2Q1Q0 = 000 will repeat after _______ number of cycles of the clock CLK.

Question 16

In the circuit shown below, Q1 has negligible collector-to-emitter saturation voltage and the diode drops negligible voltage across it under forward bias. If  is

is  X and Y are digital signals with 0 V as logic 0 and

X and Y are digital signals with 0 V as logic 0 and  as logic 1, the Boolean expansion for Z is

as logic 1, the Boolean expansion for Z is

Question 17

The logic function (A + B) can be expressed in terms of min terms as.

Question 18

A 3-variable truth table has a high output for the inputs: 010, 011 and 110. The Boolean expression for sum of product (SOP) can be written as

Question 19

Which one of the following is the dual form of the Boolean identity given above?

Question 20

The Boolean expression

Y = A' B' C' D + A' B C D' + A B' C' D + A B C' D'

can be minimized to

Y = A' B' C' D + A' B C D' + A B' C' D + A B C' D'

can be minimized to

Question 21

If F = X'YZ + XZ, then what will be the minimum number of literals?

Question 22

The Boolean function Y = AB + CD is to be realized using only 2-input NAND gates. The minimum number of gates required is:

Question 23

A binary full-subtractor.

Question 24

When two 16-input multiplexers drive a 2- input MUX, what is the result?

Question 25

What is the number of select lines required in a single input n-output demultiplexer?

Question 26

The following is a scheme for floating point number representation using 16 bits.

Let s, e, and m be the numbers represented in binary in the sign, exponent, and mantissa fields respectively. Then the floating point number represented is:

What is the maximum difference between two successive real numbers represent able in this system?

Let s, e, and m be the numbers represented in binary in the sign, exponent, and mantissa fields respectively. Then the floating point number represented is:

What is the maximum difference between two successive real numbers represent able in this system?

Question 27

Assuming all numbers are in 2’s complement representation, which of the following numbers is divisible by 11111011?

Question 28

What is the result of evaluating the following two expressions using three-digit floating point arithmetic with rounding?

(113. + - 111.) + 7.51

113. + (- 111. + 7.51)

(113. + - 111.) + 7.51

113. + (- 111. + 7.51)

Question 29

Consider the partial implementation of a 2-bit counter using T flip-flops following the sequence 0-2-3-1-0, as shown below.

To complete the circuit, the input X should be

To complete the circuit, the input X should be

Question 30

The initial contents of the 4-bit serial-in-parallel-out, right-shift, Shift Register shown in the figure is 0110. After three clock pulses are applied, the contents of the Shift Register will be

- 751 attempts

- 7 upvotes

- 40 comments

Jun 4GATE & PSU CS