Time Left - 15:00 mins

GATE CS 2018 - Digital Logic Quiz-11 ( Sequential Circuits-2)

Attempt now to get your rank among 1062 students!

Question 1

Consider a 4-bitJohnson counter with an initial value 1111. Then the counting sequence of this counter is:

Question 2

A semi-conductor ROM basically is

Question 3

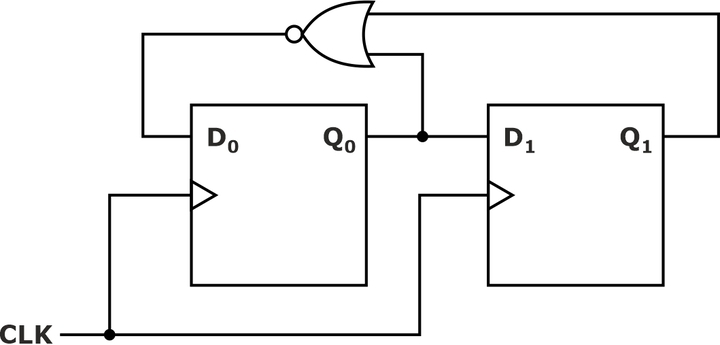

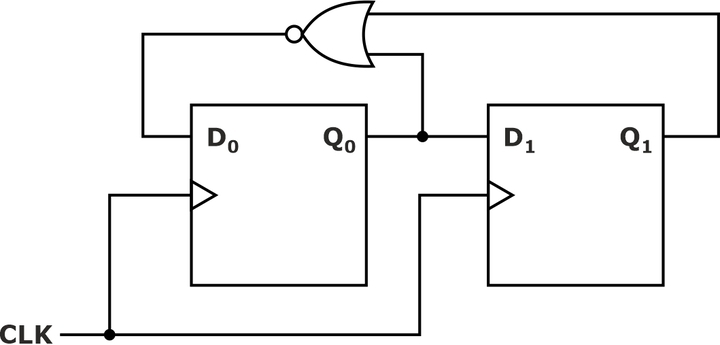

For the circuit shown, the counter state (Q0Q1) follow the sequence

Question 4

The initial contents of the 4-bit serial-in-parallel-out, right-shift, Shift Register shown in the figure is 0110. After three clock pulses are applied, the contents of the Shift Register will be

Question 5

A half adder is implemented with XOR and AND gates. A full adder is implemented with two half adders and one OR gate. The propagation delay of an XOR gate is twice that of an AND/OR gate. The propagation delay of an AND/OR gate is 1.2 microseconds. A 4-bit ripple-carry binary adder is implemented by using four full adders. The total propagation time of this 4-bit binary adder in microseconds is____________.

Question 6

A positive edge-triggered D flip-flop is connected to a positive edge-triggered JK flip-flop as follows. The Q output of the D flip-flop is connected to both the J and K inputs of the JK flip-flop, while the Qoutput of the JK flip-flop is connected to the inputof the D flip-flop. Initially, the output of the D flip-flop is set to logic one and the output of the JK flip-flop is cleared. Whichone of the following is the bit sequence (including the initial state) generated at the Q output of the JK flip-flop when the flip-flops are connected to a free-running common clock? Assume that J = K = 1 is the toggle mode and J = K = 0 is the state-holding mode of the JK flip-flop.Both the flip-flops have non-zero propagation delays.

- 1062 attempts

- 5 upvotes

- 18 comments

Oct 14GATE & PSU CS