Time Left - 15:00 mins

GATE EC 2020: Analog Quiz 3 (App update required to attempt this test)

Attempt now to get your rank among 242 students!

Question 1

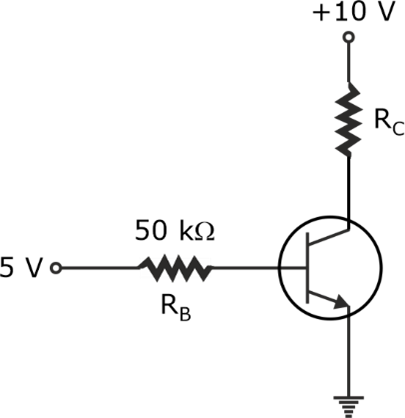

In the given figure , , the magnitude of voltage gain(

, the magnitude of voltage gain( ) will be ___

) will be ___

Question 2

In the circuit shown, the breakdown voltage and the maximum current of the Zener diode are 20 V and 60 mA, respectively. The values of R1 and RL are 200 Ω and 1 kΩ, respectively. What is the range of Vi that will maintain the Zener diode in the ‘on’ state?

Question 3

In the circuit shown, V1 = 0 and V2 = Vdd. The other relevant parameters are mentioned in the figure. Ignoring the effect of channel length modulation and the body effect, the value of Iout is ___________ mA (rounded off to 1 decimal place).

Question 4

An n-channel JFET, having a pinch-off voltage (Vp) of –5 V, shows a transconductance (gm) of 1 mA/V when the applied gate-to-source voltage (VGS) is – 3V. Its maximum transconductance (in mA/V) is

Question 5

In the circuit shown, the silicon BJT has ![]() Assume

Assume ![]() and

and ![]() Which one of the following statements is correct?

Which one of the following statements is correct?

Question 6

For the given fixed-bias configuration, determine the parameters re & ro for its equivalent re model of the transistor, if the input impedance of the network is 1 kΩ and the output impedance is 4 kΩ.

- 242 attempts

- 3 upvotes

- 1 comment

Jul 5ESE & GATE EC